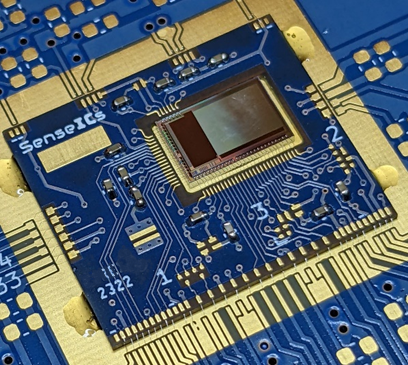

This cutting-edge MWIR event-based ROIC is designed to deliver ultra-low latency, high sensitivity, and reconfigurable pixel architectures for next-generation infrared sensing. Our ROIC integrates two advanced 32×32 test subarrays with distinct pixel types: logarithmic and linear pixel arrays to optimize performance across varying infrared scene conditions.

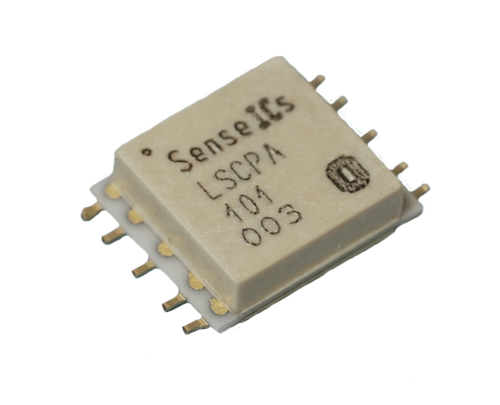

Our FLAT-32 radiation hard by design analog front end (AFE) ASIC is designed to optimize signal to noise and provide picosecond timing in detecting signals from a wide range of radiation detectors. The 32-channel linear array architecture is ideal for use in medical imaging and radiation detection applications and is robust enough to be resilient against extreme total ionizing dose and single event effects.

A one-shot HDR ROIC for eSWIR and MWIR imaging designed with the capabilities to capture high dynamic range images at low c-swap. The HDR ROIC adapts to different signal levels within a scene to provide unparalleled intraframe dynamic range. The HDR ROIC also takes advantage of Received Signal Strength Indicator (RSSI) technology to capture coarse digital images to enable event detection, smart windowing, and compressive sensing with lower power and less data transmitted.

A reconfigurable direct time-of-flight measurement System on-a-Chip (SoC) using pulsed laser for airborne & spaceborne cloud profiling and altimetry applications. This radiation hard by design detection and ranging SoC was developed to advanced long-range LiDAR ASICs featuring on-chip histogramming. Each channel in this 8-channel SoC can be configured independently to work with SPADs or linear APDs.

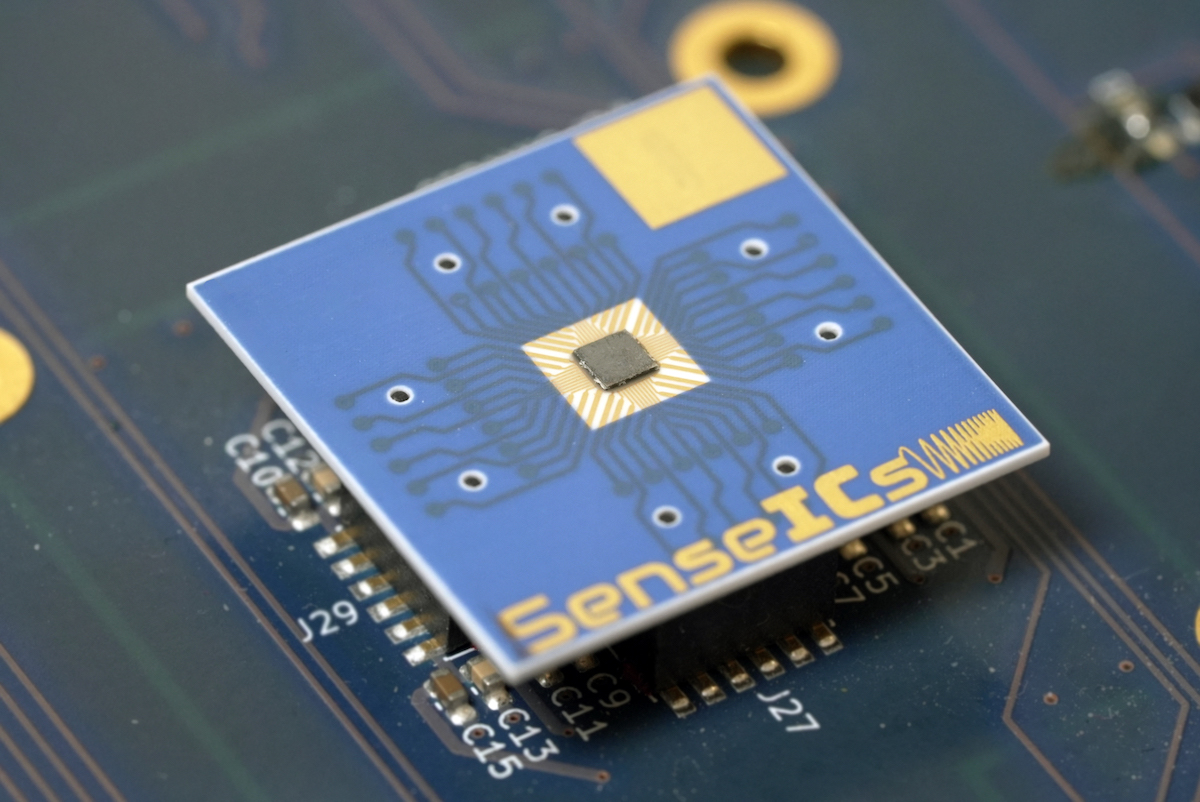

SenseICs develops advanced-node Integrated Circuits (ICs) that function as plug-and-play benchmarks for trusted microelectronics research. Our silicon-verified, multi-generational designs are engineered to enable exploration of second-order effects, hardware security, and system reliability. These ICs are actively leveraged in research initiatives addressing the evolving challenges of microelectronic assurance and innovation within the domestic IC supply chain.

As high data rate wireless communication systems are developed for 5G, there is an increasing need for capable broadband power amplifiers. For communication systems to be viable, the Power Amplifiers must remain power efficient while accommodating linearity requirements of higher order modulation. Our goal is to provide an unparalleled low size, weight, power, and cost transmitter capable of operation across the entire L, S, and C radio frequency bands.